# **CAPZero** Family

# Zero<sup>1</sup> Loss Automatic X Capacitor Discharge IC

# **Product Highlights**

- Blocks current through X capacitor discharge resistors when AC voltage is connected

- Automatically discharges X capacitors through discharge resistors when AC is disconnected

- Simplifies EMI filter design larger X capacitor allows smaller inductive components with no change in consumption

- Only two terminals meets safety standards for use before or after system input fuse

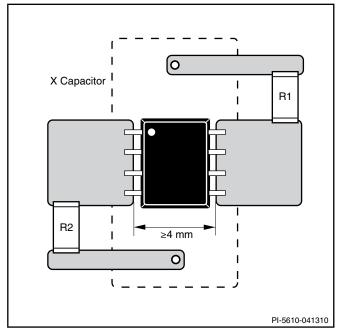

- >4 mm creepage on package and PCB

- Self supplied no external bias required

- High common mode surge immunity no external ground connection

- High differential surge withstand 1000 V internal MOSFETs

# **EcoSmart<sup>™</sup>**– Energy Efficient

<5 mW consumption at 230 VAC for all X capacitor values</li>

# Applications

- All ACDC converters with X capacitors >100 nF

- Appliances requiring EuP Lot 6 compliance

- Adapters requiring ultra low no-load consumption

- All converters requiring very low standby power

# Description

When AC voltage is applied, CAPZero<sup>™</sup> blocks current flow in the X capacitor safety discharge resistors, reducing the power loss to less than 5 mW, or essentially zero<sup>1</sup> at 230 VAC. When AC voltage is disconnected, CAPZero automatically discharges the X capacitor by connecting the series discharge resistors. This operation allows total flexibility in the choice of the X capacitor to optimize differential mode EMI filtering and reduce inductor costs, with no change in power consumption.

Designing with CAPZero is simply a matter of selecting the appropriate CAPZero device and external resistor values in Table 1 for the X capacitor value being used. This design choice will provide a worst case RC time constant, when the AC supply is disconnected, of less than 1 second as required by international safety standards.

The simplicity and ruggedness of the two terminal CAPZero IC makes it an ideal choice in systems designed to meet EuP Lot 6 requirements.

The CAPZero family has two voltage grades: 825 V and 1000 V. The voltage rating required depends on surge requirement and circuit configuration of the application. See Key Applications Considerations section for details.

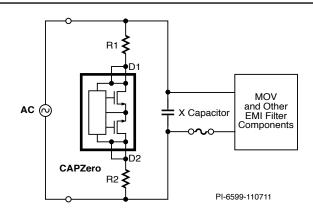

Figure 1. Typical Application – Not a Simplified Circuit.

Component Selection Table

| <b>Product</b> <sup>4</sup> | BV <sub>DSS</sub> | Maximum Total<br>X Capacitance | Total Series<br>Resistance<br>(R1 + R2) |  |

|-----------------------------|-------------------|--------------------------------|-----------------------------------------|--|

| CAP002DG                    | 825 V             | <500 nF                        | 1.5 MQ                                  |  |

| CAP012DG                    | 1000 V            | ≥300 IIF                       | 1.5 M02                                 |  |

| CAP003DG                    | 825 V             | 750 nF                         | 1.02 MΩ                                 |  |

| CAP013DG                    | 1000 V            | 750 11                         |                                         |  |

| CAP004DG                    | 825 V             | 1E                             | 780 kΩ                                  |  |

| CAP014DG                    | 1000 V            | 1 μF                           |                                         |  |

| CAP005DG                    | 825 V             | 1 5 5                          | <b>480</b> kΩ                           |  |

| CAP015DG                    | 1000 V            | 1.5 μF                         |                                         |  |

| CAP006DG                    | 825 V             | 2E                             | 360 kQ                                  |  |

| CAP016DG                    | 1000 V            | 2 μF                           | 200 K75                                 |  |

| CAP007DG                    | 825 V             | 25E                            | 300 kΩ                                  |  |

| CAP017DG                    | 1000 V            | 2.5 μF                         |                                         |  |

| CAP008DG                    | 825 V             | 3.5 μF                         | 200 kQ                                  |  |

| CAP018DG                    | 1000 V            | 5.5 μΓ                         | 200 K12                                 |  |

| CAP009DG                    | 825 V             | E.,E                           | 150 k $\Omega^3$                        |  |

| CAP019DG                    | 1000 V            | 5 μF                           | 100 K75                                 |  |

Table 1. Component Selection Table.

Notes:

- 1. IEC 62301 clause 4.5 rounds standby power use below 5 mW to zero.

- 2. Values are nominal. RC time constant is <1 second with  $\pm 20\%$  X capacitor and  $\pm 5\%$  resistance from these nominal values.

- Lowest value of discharge resistor that can be used.

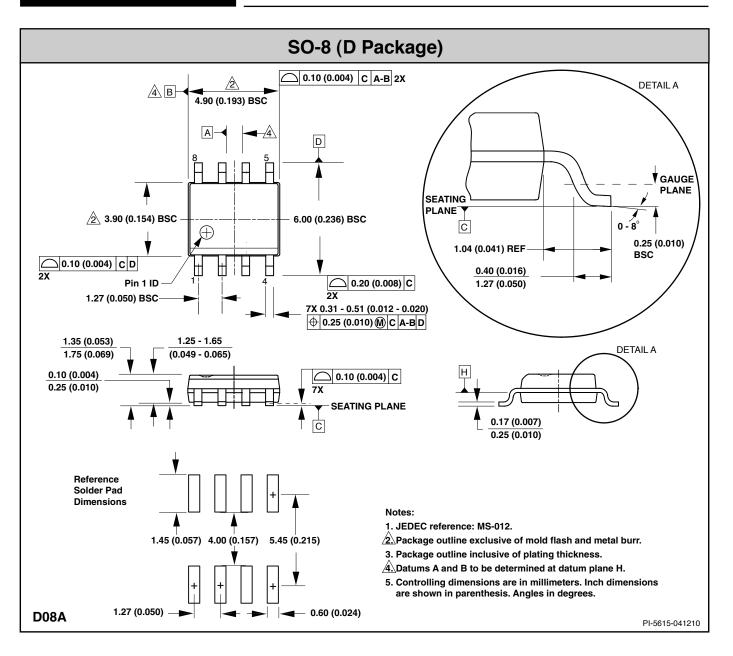

4. Packages: D: SO-8.

# **Pin Functional Description**

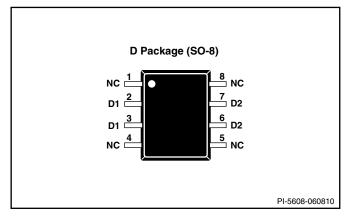

The pin configuration of Figure 2 ensures that the width of the SO-8 package is used to provide creepage and clearance distance of over 4 mm.

Although electrical connections are only made to pins 2, 3, 6 and 7, it is recommended that pins 1-4 and pins 5-8 are coupled together on the PCB – see Applications Section.

Figure 2. Pin Configuration.

# **Key Application Considerations**

# **Breakdown Voltage Selection**

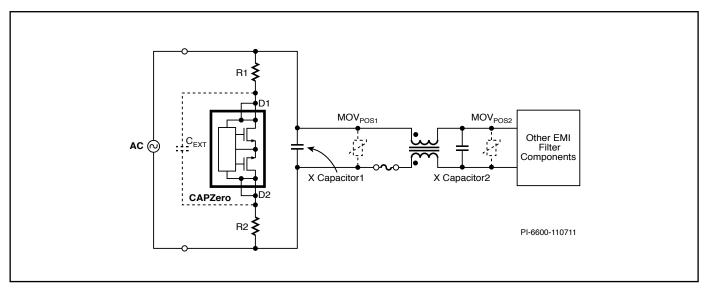

Figure 3 illustrates possible system configurations influencing the choice of CAPZero breakdown voltage. The system configuration variables include the placement of the system MOV and X capacitor(s) as well as the differential surge voltage specifications of the application.

As shown in Table 1, each device in the CAPZero family has a 825 V or 1000 V option. For applications where the system MOV is placed in position 1 ( $MOV_{POS1}$  in Figure 3), the 825 V option will typically provide adequate voltage withstand for surge requirements up to 3 kV or more. The 1 kV CAPZero would be recommended for higher surge requirements or if additional voltage margin is required.

For MOV placement that is not directly across the X Capacitor1 (for example MOV<sub>POS2</sub> in Figure 3) the 1000 V CAPZero devices can be used up to a surge specification of 1.5 kV. For differential surge voltage specifications of >1.5 kV it is recommended that the MOV is always placed in the location shown in Figure 3 as  $MOV_{POS1}$ .

It is always recommended that the peak voltage between terminals D1 and D2 of CAPZero is measured during surge tests in the final system. Measurements of peak voltage across CAPZero during surge tests should be made with oscilloscope probes having appropriate voltage rating and using an isolated supply to the oscilloscope to avoid ground currents influencing measurement results. When making such measurements, it is recommended that 50 V engineering margin is allowed below the breakdown voltage specification (for example 950 V with the 1000 V CAPZero).

If the measured peak Drain voltage exceeds 950 V, an external 1 kV ceramic capacitor can be placed between D1 and D2 terminals to attenuate the voltage applied between the CAPZero terminals during surge. Please refer to the Application Note AN-48 for the details. This optional external capacitor placement is shown as  $C_{\text{EXT}}$  in Figure 3. It should be noted that use of an external capacitor in this way will increase power consumption slightly due to the  $C_{\text{EXT}}$  charge/discharge currents flowing in R1 and R2 while AC is connected.

# **PCB Layout and External Resistor Selection**

Figure 4 shows a typical PCB layout configuration for CAPZero. The external resistors in this case are divided into two separate surface mount resistors to distribute loss under fault conditions – for example where a short-circuit exists between CAPZero terminals D1 and D2. R1 and R2 values are selected according to Table 1.

Under a fault condition where CAPZero terminals D1 and D2 are shorted together, each resistor will dissipate a power that can be calculated from the applied AC voltage and the R1 and R2 values. For example in an application using CAP004 or CAP014, R1=R2=390 k $\Omega$ . If CAPZero is shorted out at 265 VAC R1 and R2 will each dissipate 45 mW.

Resistors R1 and R2 should also be rated for 50% of the system input voltage again to allow for the short-circuitry of CAPZero D1 to D2 pins during single point fault testing.

Figure 3. Placement Options of MOV and C<sub>EXT</sub>

# CAPZero

If lower dissipation or lower voltage across each resistor is required during fault tests, the total external resistance can be divided into more discrete resistors, however the total resistance must be equal to that specified in Table 1.

# Safety

CAPZero meets safety requirements even if placed before the system input fuse. If a short-circuit is placed between D1 and D2 terminals of CAPZero, the system is identical to existing systems where CAPZero is not used.

With regard to open circuit tests, it is not possible to create a fault condition through a single pin fault (for example lifted pin test) since there are two pins connected to each of D1 and D2. If several pins are lifted to create an open circuit, the condition is identical to an open circuit X capacitor discharge resistor in existing systems where CAPZero is not used. If redundancy against open circuit faults is required, two CAPZero and R1 / R2 configurations can be placed in parallel.

# **Discharge Operation**

To meet the safety regulations, when the AC supply is disconnected, CAPZero will discharge the X capacitor to the safety extra low voltage (SELV) levels according to the above functional description. Although there are no specific safety requirements below SELV, CAPZero still continues the discharge until the X capacitor is fully discharged. As such CAPZero can be safely used at low input voltages such as the common industrial 18 VAC and 24 VAC supply rails while retaining X capacitor discharge when the AC source is disconnected.

Figure 4. Typical PCB Layout.

# Absolute Maximum Ratings<sup>(4)</sup>

| DRAIN Pin Voltage <sup>(1)</sup>  | CAP002-CAP009 | 825 V           |

|-----------------------------------|---------------|-----------------|

|                                   | CAP012-CAP019 | 1000 V          |

| DRAIN Peak Current <sup>(2)</sup> | CAP002/CAP012 | 0.553 mA        |

|                                   | CAP003/CAP013 | 0.784 mA        |

|                                   | CAP004/CAP014 | 1.026 mA        |

|                                   | CAP005/CAP015 | 1.667 mA        |

|                                   | CAP006/CAP016 | 2.222 mA        |

|                                   | CAP007/CAP017 | 2.667 mA        |

|                                   | CAP008/CAP018 | 4.000 mA        |

|                                   | CAP009/CAP019 | 5.333 mA        |

| Storage Temperature               |               | 65 °C to 150 °C |

| Lead Temperature <sup>(3)</sup>   |               | 260 °C          |

# Notes:

1. Voltage of D1 pin relative to D2 pin in either polarity.

- 2. The peak DRAIN current is allowed while the DRAIN voltage is simultaneously less than 400 V.

- 3. 1/16 in. from case for 5 seconds.

- 4. The Absolute Maximum Ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect product reliability.

# **Thermal Resistance**

Thermal Resistance: D Package1:

| B) |

|----|

| n) |

| p) |

|    |

## Notes:

1. Reference thermal resistance test conditions: JEDEC JESD51-3, SEMI Test Method #G43-87, and MIL-STD-883 Method 10121.1.

| Parameter                                  | Symbol              | <b>Conditions</b><br>$T_A = -10$ to 105 °C<br>(Unless Otherwise Specified) | Min  | Тур | Max  | Units |

|--------------------------------------------|---------------------|----------------------------------------------------------------------------|------|-----|------|-------|

| <b>Control Functions</b>                   |                     |                                                                            |      |     |      |       |

| AC Removal<br>Detection Time               | t <sub>DETECT</sub> | Line Cycle Frequency 47-63 Hz                                              |      | 22  | 31.4 | ms    |

| Drain Saturation<br>Current <sup>A,B</sup> | I <sub>dsat</sub>   | CAP002/012                                                                 | 0.25 |     |      | - mA  |

|                                            |                     | CAP003/013                                                                 | 0.37 |     |      |       |

|                                            |                     | CAP004/014                                                                 | 0.48 |     |      |       |

|                                            |                     | CAP005/015                                                                 | 0.78 |     |      |       |

|                                            |                     | CAP006/016                                                                 | 1.04 |     |      |       |

|                                            |                     | CAP007/017                                                                 | 1.25 |     |      |       |

|                                            |                     | CAP008/018                                                                 | 1.88 |     |      |       |

|                                            |                     | CAP009/019                                                                 | 2.5  |     |      |       |

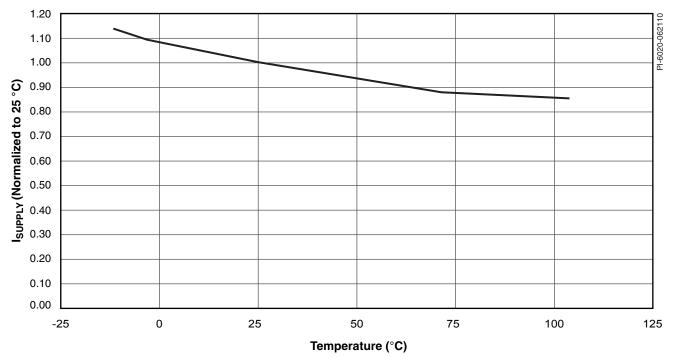

| Supply Current                             | I <sub>SUPPLY</sub> | T <sub>A</sub> = 25 °C                                                     |      |     | 21.7 | μA    |

Notes:

A. Saturation current specifications ensure a natural RC discharge characteristic at all voltages up to 265 VAC pk with the external resistor values specified in Component Selection Table 1.

B. Specifications are guaranteed by characterization and design.

# **Typical Performance Characteristics**

Figure 5.  $I_{SUPPLY}$  vs. Temperature.

CAPZero

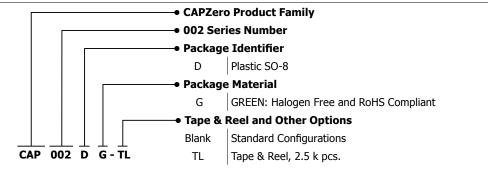

# **Part Ordering Information**

| Revision | Notes                                                                                                                      | Date     |

|----------|----------------------------------------------------------------------------------------------------------------------------|----------|

| А        | Code A release.                                                                                                            | 04/14/10 |

| В        | Updated $I_{SUPPLY}$ condition. Added figure 5. Parameter $T_{DETECT}$ was updated.                                        | 06/08/10 |

| С        | Updated Table 1. Updated Note 1 in Table 1. Added "Discharge Operation" paragraph. Updated Absolute Maximum Ratings Table. | 02/11    |

| С        | Added Maximum Junction Temperature specification.                                                                          | 04/11    |

| D        | Updated Figures 1 and 3.                                                                                                   | 11/07/11 |

| Е        | Added R <sub>DS(ON)</sub> max. at 105 °C for CAPZero parts.                                                                | 03/12    |

| Е        | Added Thermal Resistance section.                                                                                          | 09/16/13 |

| F        | Updated with new Brand Style.                                                                                              | 05/15    |

| G        | Removed R <sub>DS(ON)</sub> information.                                                                                   | 07/15    |

| Н        | Added Note 3 in Table 1. Updated text on page 2, 3rd paragraph right column.                                               | 03/18    |

# For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at www.power.com/ip.htm.

#### Life Support Policy

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The PI loao, TOPSwitch, TinySwitch, SENZero, SCALE, SCALE-iDriver, SCALE-iFlex, Ospeed, PeakSwitch, LYTSwitch, LinkZero, LinkSwitch, InnoSwitch, HiperTFS, HiperPFS, HiperLCS, DPA-Switch, CAPZero, Clampless, EcoSmart, E-Shield, Filterfuse, FluxLink, StakFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2018, Power Integrations, Inc.

#### **Power Integrations Worldwide Sales Support Locations**

# World Headquarters

5245 Hellyer Avenue San Jose, CA 95138, USA Main: +1-408-414-9200 Customer Service: Worldwide: +1-65-635-64480 Americas: +1-408-414-9621 e-mail: usasales@power.com

# China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 e-mail: chinasales@power.com

#### China (Shenzhen)

17/F, Hivac Building, No. 2, Keji Nan Bangalore-560052 India 8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 e-mail: chinasales@power.com

Germany (AC-DC/LED Sales) Lindwurmstrasse 114 D-80337 München Germany Phone: +49-89-5527-39100 e-mail: eurosales@power.com

Germany (Gate Driver Sales) HellwegForum 1 59469 Ense Germany Tel: +49-2938-64-39990 e-mail: igbt-driver.sales@power.com

## India

#1, 14th Main Road Vasanthanagar Phone: +91-80-4113-8020 e-mail: indiasales@power.com

#### Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701 e-mail: eurosales@power.com

#### Japan

Yusen Shin-Yokohama 1-chome Bldg. Taiwan 1-7-9, Shin-Yokohama, Kohoku-ku Yokohama-shi, Kanagawa 222-0033 Japan Phone: +81-45-471-1021 e-mail: japansales@power.com

# Korea

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610 e-mail: koreasales@power.com

#### Singapore

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160 e-mail: singaporesales@power.com

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 e-mail: taiwansales@power.com

# UK

Building 5, Suite 21 The Westbrook Centre Milton Road Cambridge CB4 1YG Phone: +44 (0) 7823-557484 e-mail: eurosales@power.com